Chiplet,真的万事俱备了吗?

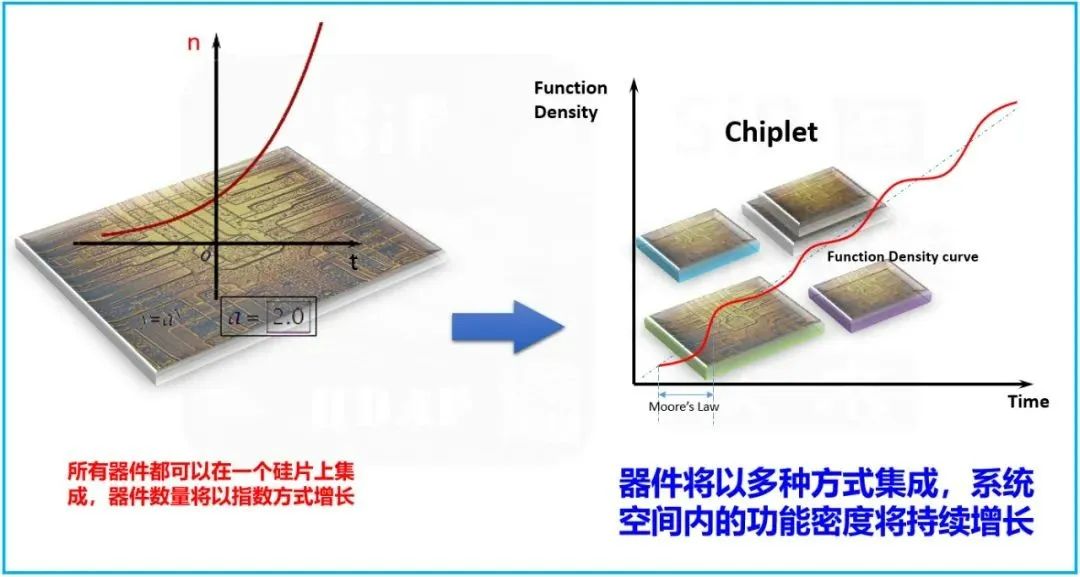

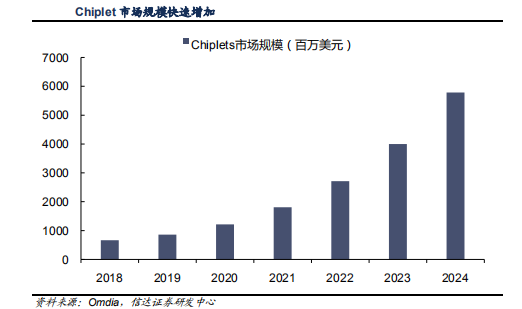

Chiplet:延续摩尔定律的新法宝

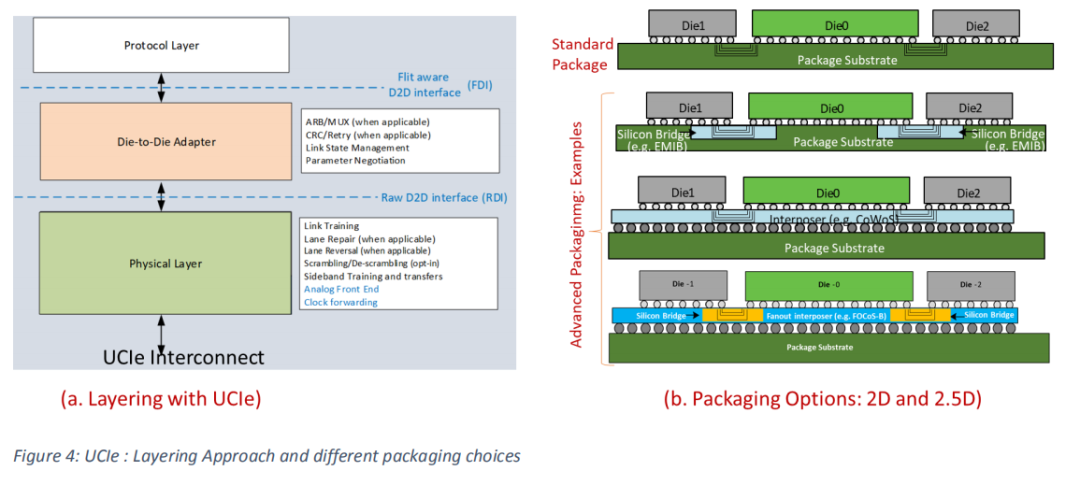

UCIe:Chiplet 互联标准的关键一步

Chiplet万事俱备了吗?

先进封装

芯片测试

系统设计复杂度

EDA工具等软件配合

Chiplet对于中国产业的机会

写在最后

UCIe产业联盟当前为什么没有EDA厂商? 苹果和英伟达为何没有参与其中? 是否允许中国厂商参与其中?如果未来出现禁令相关问题,能否规避? UCIe如何落实“开放”二字? 是否会有专门的UCIe IP对外授权,帮助其它厂商加入生态? ...

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2977内容,欢迎关注。

推荐阅读

★苹果发布1140亿晶体管M1 Ultra:12年自研34颗处理器

半导体行业观察

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!

收录于话题 #李晨光

38个下一篇 谁正在赢下芯片产能竞赛?

发送给作者