来源:内容来自半导体行业观察(ID:icbank)综合,谢谢。

半导体行业观察最有深度的半导体新媒体,实讯、专业、原创、深度,50万半导体精英关注!专注观察全球半导体最新资讯、技术前沿、发展趋势。《摩尔精英》《中国集成电路》共同出品,欢迎订阅摩尔旗下公众号:摩尔精英MooreElite、摩尔芯闻、摩尔芯球

2533篇原创内容

公众号

苹果近期发布的Mac Studio采用了简约设计,与其他 Apple 设备等现代工作站相比,显得相当简陋。但这些设计隐藏的是苹果庞大的 M1 Ultra 处理器封装,它占据了主板约四分之一的空间、一个非常复杂的电压调节模块 (VRM) 和两个用户可访问的 SSD。Apple 正在向最终用户交付 Mac Studio 系统,一些最终用户会剖析这些 PC 以找出它们的内部设计和架构。事实上,Mac Studio 也有很多值得关注的地方。正如第一个拆解 Mac Studio 的Max Tech YouTube 频道所披露的那样,Apple 的 Mac Studio 是高精度工程的杰作,它由安装在相对较小的印刷电路板上的数百个组件组成。

芯片观察 ,

芯片观察 ,苹果Mac studio首拆,看看apple 1 ultra的尺寸

视频号

Apple 的 M1 Ultra 处理器 是基于TSMC 的 CoWoS-S(带有硅中介层的晶圆上芯片)实现的,这是一个基于 2.5D 中介层封装两个 M1 Max 系统级芯片 (SoC)的技术。这两个 SoC 具有内存子系统。它们使用该公司的 UltraFusion 处理器间互连连接在一起,该互连提供 2.5 TB/s 的带宽,足以将两个 GPU 和两个内存子系统作为一个提供给操作系统。鉴于这样的架构,我们预计 Apple 的 M1 Ultra 会非常庞大。事实上,M1 Ultra 也是巨大的。如上图所示,与 AM4 规格的 AMD Ryzen 处理器相比,苹果新芯片大了差不多三倍。一个 M1 Ultra 占据了 Mac Studio 主板的 25% 左右。由于我们是两个 M1 Max,因此 M1 Ultra 有两个相当复杂的 VRM,可以为这个怪兽芯片提供高质量的电源保证,让它在高时钟下运行。当然,这意味着我们正在处理一个非常复杂的主板,但如果您需要最大限度地提高性能,这就是要走的路。由于 M1 Ultra 耗电大,发热量大,所以它需要非常先进的双风扇散热系统也就不足为奇了。冷却系统从处理器顶部和底部带走热量,这很好地了解地处理设备产生的热量。但是,虽然 M1 Ultra 对于 Apple 用户来说看起来很大,但新的 Mac Studio 内部还有一个更大的东西。Apple 通过 M1 Ultra 加入 3D-Fabric 产品组合?

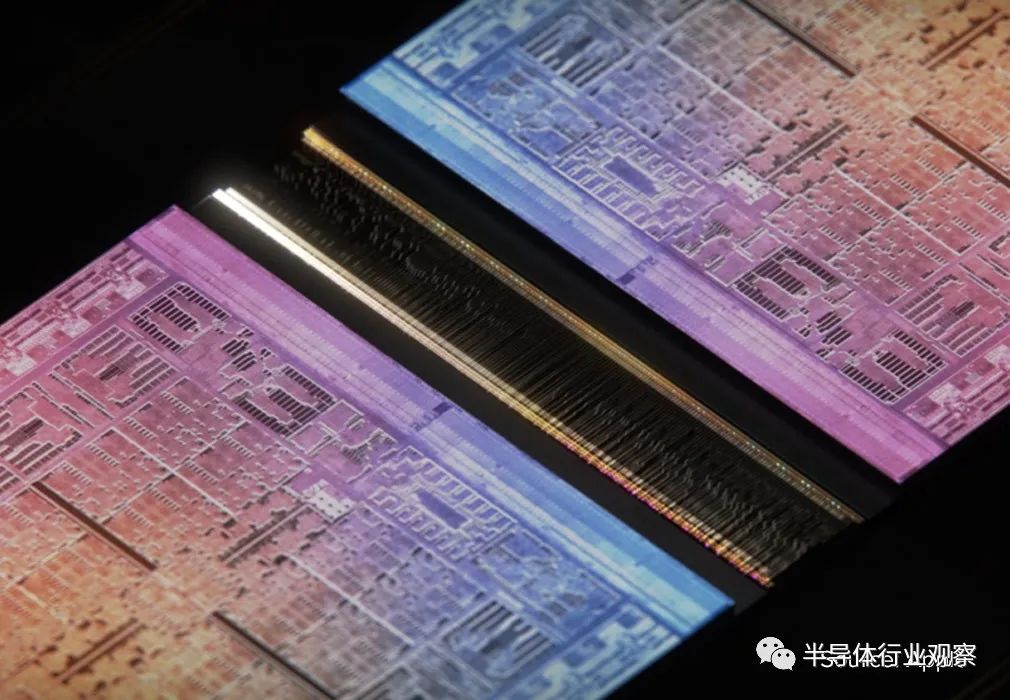

“M1 Ultra 是 Apple 芯片的另一个改变游戏规则的产品,它将再次震撼 PC 行业。通过将两个 M1 Max 芯片与我们的 UltraFusion 封装架构相连接,我们能够将 Apple 芯片扩展到前所未有的新高度,”Apple 硬件技术高级副总裁 Johny Srouji 说道。所以——“用我们的 UltraFusion 封装架构连接两个 M1 Max 芯片”——用听起来像中介层或硅桥的东西连接两个处理器芯片。在演讲中,Johny Srouji 说“UltraFusion 架构使用了一种硅中介层,其连接密度是任何可用技术的两倍”。M1 Max 的尺寸约为 19.05 x 22.06 毫米或 420.2 平方毫米,因此即使die边缘接触die边缘,台积电 CoWoS 型中介层的最小尺寸为 840 平方毫米,这正好处于光罩限制极限。那是很多硅,(即费用),所以现在我们有了英特尔的 EMIB等桥接技术,这似乎更有可能。谈话中的一个惊喜是 M1 Max 已经设计了片上互连电路。当我们看的时候,它在die的底部:图 3. 采用片上互连电路设计的 Apple M1 MAX APL1105 处理器。在我们的 DFR-2111-801 平面图分析中,我们保守地将该区域标记为数字逻辑块;现在我们知道了它们的功能。仔细看:图 4. Apple M1 MAX APL1105 die照片。台积电宣布了两个版本的硅桥技术,InFO_LSI 和 CoWoS-L。图 5. TSMC InFO_LSI 和 CoWoS-L。我们没有 CoWoS-L 的具体数字,但 InFO_LSI 凸块焊盘间距指定为 25 µm,与我们在 M1 Max 的互连区域中看到的相同。因此,了解了 Apple 和 TSMC 之间的紧密关系,很容易假设他们的“UltraFusion 封装架构”至少是 InFO_LSI/CoWoS-L 的定制版本。InFO_LSI 的 RDL(再分布层)线/空间尺寸为 0.4/0.4 µm,这意味着 I/O 密度为 1250/mm/层。鉴于互连侧的芯片边缘长度超过 18 毫米,这为我们提供了超过 20,000 个潜在的 I/O,远远超过 Srouji 引用的 10,000 个。相比之下,英特尔的 EMIB 为 250/mm/层或更大,而现有的 55-µm 凸块间距;当然,他们将致力于提高这种密度。合并后的 SoC 拥有 1140 亿个晶体管,将 M1 Max 加倍使其成为 20 核 CPU、64 核 GPU 和 32 核神经引擎的一部分。它可以构建高达 128GB 的 LPDDR5-6400 统一内存,并具有规定的 800GB/s 内存带宽。据称,这 10,000 个信号可在两个 M1 Max 芯片之间提供 2.5TB/s 的低延迟、处理器间带宽。这使得 M1 Ultra 可以作为一个芯片运行并被软件识别,无需为新结构重写代码。macOS Monterey 专为 Apple 芯片设计,将利用 M1 Ultra 的额外 CPU、GPU 和内存功能。

★ 点击文末【阅读原文】,可查看本篇原文链接!

半导体芯闻您的半导体行业内参,每日精选8条全球半导体产业重大新闻解读,一天只花10分钟,享受CEO的定制内容服务。与30万半导体精英一起,订阅您的私家芯闻秘书!欢迎订阅摩尔精英旗下更多公众号:摩尔精英、半导体行业观察、摩尔App

252篇原创内容

公众号

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2985内容,欢迎关注。

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!