博士Review | 博士创『芯』说第十五期—贾海昆:高性能毫米波振荡器设计技术

ISSCC 2022特别篇 第二场

4月7日上午,博士创『芯』说第十五期——【ISSCC 2022 特别篇】的第二场线下活动在荷清大厦举办。来自清华大学集成电路学院的助理教授贾海昆博士来到中心,为大家带来题为“性能毫米波振荡器设计技术”的学术报告。来自清华大学集成电路学院的姜琪同学主持了本场线下活动。报告由腾讯会议与蔻享学术平台同时直播,收到了老师同学们的热烈欢迎。报告后,主讲嘉宾与线上线下的百余位师生针对VCO设计中的热点难点、技术发展脉络及其在不同应用场景与不同纳米工艺节点下的特点进行了热烈地交流讨论。

为了跨越时空障碍,丰富拓展大家的学习渠道,我们邀请贾海昆博士为本期报告作文字版详细评述,并于文末附上精彩问答集锦、博士推荐阅读与报告视频回放。让我们通过文字与视频,与贾海昆博士一起回顾本场特别篇的精彩内容吧!

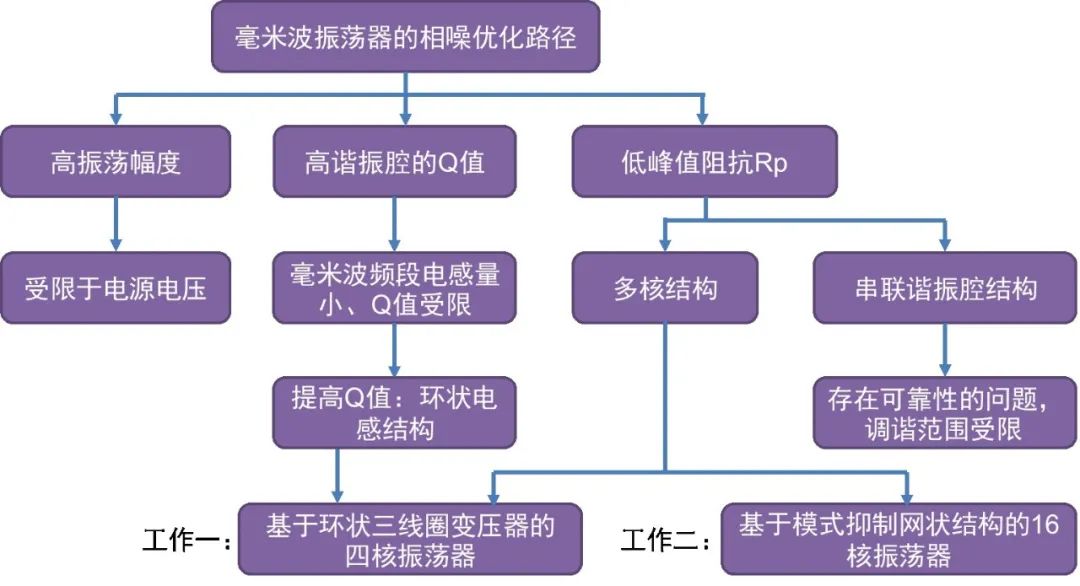

5G毫米波通信、高速串行接口和高速高精度ADC等系统对片上振荡器的性能提出了极高的要求。以载波为80GHz的256QAM调制信号为例,其要求振荡器在1MHz处的相位噪声低于-108dBc/Hz,对于硅基工艺依然极具技术挑战性。振荡器的相位噪声可以使用经典的Leeson公式进行描述:

其中,振荡幅度A、谐振腔的品质因子Q和峰值阻抗Rp为三个关键的设计变量。其中,振荡幅度受限于电源电压。而在毫米波频段,振荡器所需的电感急剧减小,谐振腔的品质因子Q受到小电感量的限制。峰值阻抗Rp则代表了振荡器相位噪声和功耗的折中关系。小的Rp可以提高相位噪声性能,但是需要消耗更大的电流去维持恒定的振荡幅度。有两种技术方案可以有效的降低峰值阻抗Rp。第一种是串联谐振技术。串联谐振利用RLC串联电路在谐振点的低阻特性,可大大降低相位噪声。但串联谐振腔在电容两端会产生Q倍于电源电压的信号幅度,会产生可靠性问题,限制了振荡器的调谐范围。第二种低Rp是多核振荡器技术。多核振荡器通过将N个独立的振荡器耦合在一起,使得Rp变为原有的1/N,可将相位噪声性能提高10log(N) dB。我们针对多核振荡器技术展开研究,提出了适合用于毫米波频段的多核振荡器拓扑结构,包括基于耦合三线圈的四核振荡器和基于模式抑制MESH结构的16核振荡器。该技术将硅基毫米波振荡器的性能提升到了新的高度。

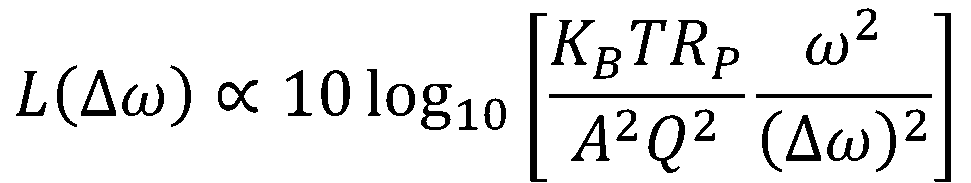

基于环形耦合三线圈的毫米波四核振荡器

本工作以”A 60GHz 186.5dBc/Hz FoM Quad-Core Fundamental VCO Using Circular Triple-Coupled Transformer with No Mode Ambiguity in 65nm CMOS“发表在ISSCC 2021之上。针对当前基频振荡器的相位噪声性能受限于硅基工艺晶体管的有限增益和片上电感的插入损耗,难以满足5G毫米波通信中高阶数字调制需求的挑战,针对毫米波振荡器受到电感品质因子影响这个问题,我们提出环状的电感结构,消除了小尺寸电感内径负耦合,大大提高了电感的品质因子。同时,采用三线圈变压器将4个振荡器核耦合在一起,使相位噪声得到额外6dB的降低。团队发布的振荡器采用65nm的CMOS工艺设计和制造,振荡在60GHz,在1MHz频偏处的相位噪声为-104.7dBc/Hz。该设计还具备简洁、面积小、对频率失配鲁棒性好等特点。实际测试中,当核与核之间的频率失配高达14%时,其相位噪声的恶化仅仅为0.61dB。

基于环形三线圈的四核VCO版图照片及其性能比较

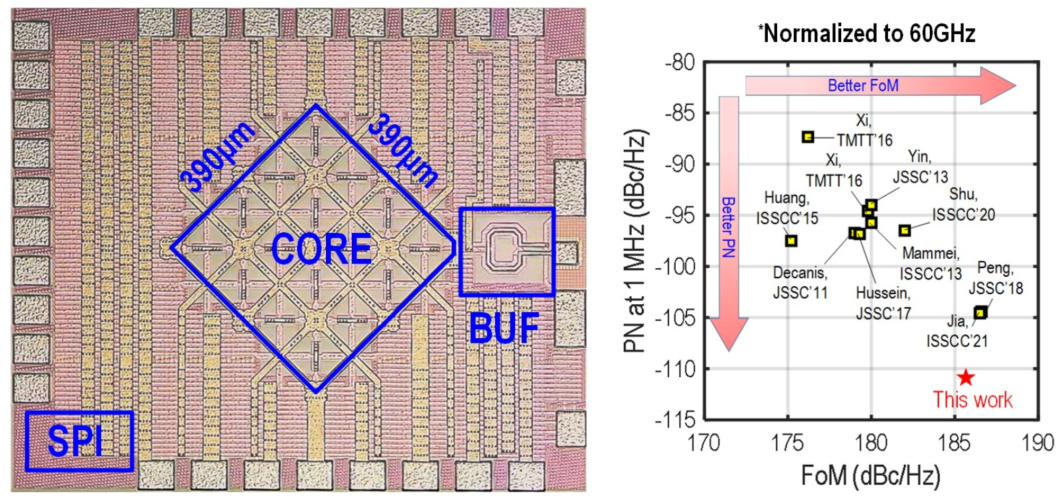

基于模式抑制MESH结构的毫米波16核振荡器

本工作以“A 53.6-to-60.2GHz Many-Core Fundamental Oscillator with Scalable Mesh Topology Achieving -136.0dBc/Hz Phase Noise at 10MHz Offset and 190.3dBc/Hz Peak FoM in 65nm CMOS”为题发表在ISSCC 2022之上。在我们团队2021年ISSCC的四核VCO的工作之上,我们进一步提高了硅基毫米波振荡器的性能指标。在多核耦合机制上,我们提出了基于模式抑制的多核耦合技术,相比于传统的电阻耦合多核结构,该结构可简化耦合网络连线,更适合于多核的扩展。在电路拓扑结构上,我们提出了MESH多核拓扑结构,有效的减小了芯片面积,从而降低了电源压降对振荡器的性能影响。最终采用65nm的CMOS工艺实现的16-核基频振荡器在1MHz频偏处的相位噪声为-111.7dBc/Hz,比文献中相似频段的现有最低水平降低了7.0dB。

毫米波多核基频振荡器芯片照片及性能比较

3. Franceschin, A., et al., Series-Resonance BiCMOS VCO with Phase Noise of -138dBc/Hz at 1MHz offset from 10GHz and -190dBc/Hz FoM. in 2022 IEEE International Solid-State Circuits Conference (ISSCC). 2022.

A1:对于4核的VCO来说,电感中间是没有填dummy的。对于16核的VCO我们在中间填了滤波电容,但它没有过那个全部的密度规则。因为我们用的是65纳米,65纳米它还能够容忍这种,流片回来也没有什么问题。如果密度规则一定要过的话,那就必须得在电感中间去填dummy了。如果大家填的比较细致,就尽量避免在电感线圈正下方去填。那这样dummy对电感的Q值影响很小,可能降低10%左右。但直接拿所有dummy去仿是不太可能的,这个仿的资源消耗太大。那我们其实是把dummy画的更大,把它等效为一个柱子,这样它比实际情况更差。

Q2:两个 core 之间连线寄生电阻几十欧姆可以吗?

A2:如果你是用前面那种电阻耦合的方式,几十欧寄生电阻应该够了。因为那个它只需要那个电阻的作用是把两个VCO把它拉在一起。但在他同步上之后,那里面是没有电流的。但是考虑到这两个核之间可能存在频偏,那这个电阻是需要特别考虑的,就如果频偏比较大,那这个电阻就要相对大一点。如果我们只做两核或者四核这种比较小的核数,我觉得几十欧都够了。那如果我们做更多的核数,这个电阻可能要更强。比如说调到几欧,这个可能根据实际仿真去判断。

Q3:请问下如何理解非耦合线形式的振荡器能够降低相噪的原理?

A3:可以这样理解。如果两个核放在一起,中间没有我们这种模式抑制的耦合,那这两个核会自由震荡。它们的相噪声是不相关的,它们的信号相位也是不相关的,那我当我们把它耦合在一起的时候就多了一个机制去让他们的相位同步,让他们的信号相位是同步的。但噪声又是不同步的。所以每个核都对边上的一个核提供了一种作用机制让他的信号同步和噪声不同步,这样相噪得到降低。这个有点像相控阵的原理,就相控阵我们如果是两路接收机,它其实也能够让输入的噪声系数下降三dB,这个是一种形象化的理解。

Q4:VCO 仿真过程中经常出现不收敛的情况,需要反复迭代。有没有什么比较好的方法判断是模型问题还是参数设计不合理的问题?

A4:这个我们也经常遇到,尤其是做毫米波的时候,我们需要用到s参数。把s参数用在瞬态仿真里面,肯定多多少少会出现一些问题。我觉得有几个判断方法,一个就是我们用瞬态仿真,然后把那个精度设的比较高,看看它能不能起振。再一个就是我们换不同的仿真引擎,比如用PSS shooting和HB,然后去对比。另一个就是我们把s参数替换成拟合出来的几种模型,这样仿真器更好处理。通过多种方式去对比,判断是模型问题还是参数设计不合理的问题。那如果瞬态能振,或者说几种模型能振,但是s参数不能振,那很有可能就是仿真器的问题。

Q5:如果是先进工艺,无法把电路90度旋转,是否会对 VCO 间的匹配影响很大?

A5:我们目前也在28纳米下做一些多核的VCO。根据我们的测试结果,如果是第一种VCO的结构,因为它的抗耦合能力实在是非常强。从我们测试结果来看,就一个电容值调到最大,一个电容值调到最小,它都能够耦合在一起,而且相噪损失不太大。那对这种结果就是我把电路90度旋转,做两套电路。它的寄生电容的差异不会大于我们这种耦合电容,开关电容的差异。所以应该还没有问题。但如果我们用电阻耦合,那这点就要特别小心了。因为电阻耦合它抗这个频率失配能力比较弱,所以的确会对VCO的匹配造成影响。

Q6:关于 vco 调频线性度的设计有没有比较好的方法?

A6:调频线性度的话,如果我们用模拟调频,那文献中的确有一些方法,使用多个容抗管,这样它的非线性相互叠加。最后等效出一个比较好的调频线性度。那如果我们做DCO这个就要对电容去做一些设计了。电容可以用温度补偿,或者是我们把那个走线的寄生电感也考虑进去,做一些合适的分布,这样对线性度有好处。如果你要达到非常高的线性度,我觉得最后还是只能靠校准。比如说在数字域去做一个预失真,然后针对VCO调频、线性调频曲线做一个补偿。

Q7:请问多核设计如何控制功耗呢?

A7:多核设计控制功耗这个问题,我觉得就是可以从我们的设计指标去考虑,比如说我需要达到-110dbc的相噪,那我把它分成几个核,它每个核应该多少功耗。因为我们多核是一个功耗和相噪的tradeoff,所以根据我们的相噪要求,基本上就可以确定功耗。Q值决定之后,在具体实现上有一些优化的方式。第一就是电源地的走线,让它压降更小一点,然后再让多个核之间的耦合更有效率一点,降低相噪的损失,这样最后其实都反映到功耗的优化上面。

长按下方二维码,关注官方微信。

未来芯片高精尖中心

微信号:THU-ICFC