如何构建Chiplet产业生态?

文︱郭紫文

图︱网络

长期以来,半导体工艺制程始终遵循着摩尔定律持续演进,晶体管密度呈指数级增长态势,而成本却持续降低。随着先进工艺演进至3nm乃至2nm,晶体管微缩已达到物理极限,芯片性能与成本的平衡难以为继,“摩尔定律已死”的预判已经逐渐成为定论。

然而产业智能化趋势之下,算力及存储需求逐渐爆发,业界开始寻求延续摩尔定律的关键创新,围绕新工艺、新封装、新架构、新材料等趋势,半导体产业迎来新的发展契机。以先进封装为例,从2D到3D、从单片集成到异构集,芯片封装技术逐渐开始引领半导体技术的发展。其中,作为先进封装最热门的话题之一,Chiplet被认为是未来芯片制造的重要发展方向。

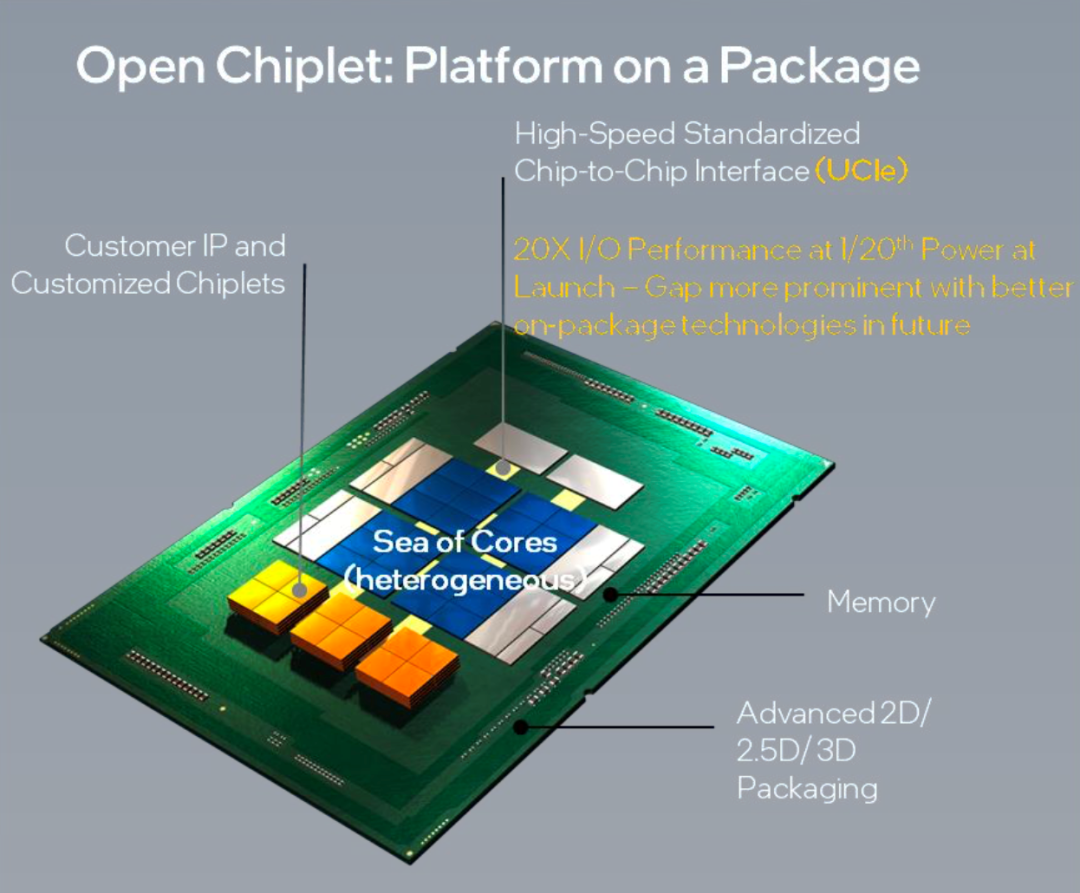

图源:UCIe白皮书

从本质上看,晶体管微缩技术陷入瓶颈,促使复杂芯片逐渐分解为若干子系统,通过标准化子系统提高设计灵活度,缩短设计周期。Chiplet可以通过封装与互联技术将这些不同工艺的模块化芯片集成在一起,进一步提高芯片制造良率,降低制造成本。

延续摩尔定律的关键

Chiplet概念最早出现于2015年,随后在2018年经由AMD推入商业化应用。作为经济学概念,摩尔定律本质上是性能与成本效益的提升。如前面所说,摩尔定律的演进已经无法支撑芯片集成规模的扩大,随着晶体管密度不断增大,工艺误差及加工缺陷愈加严重,漏电流、散热、时钟频率问题也越来越严重,从而导致芯片良率的大幅下降。

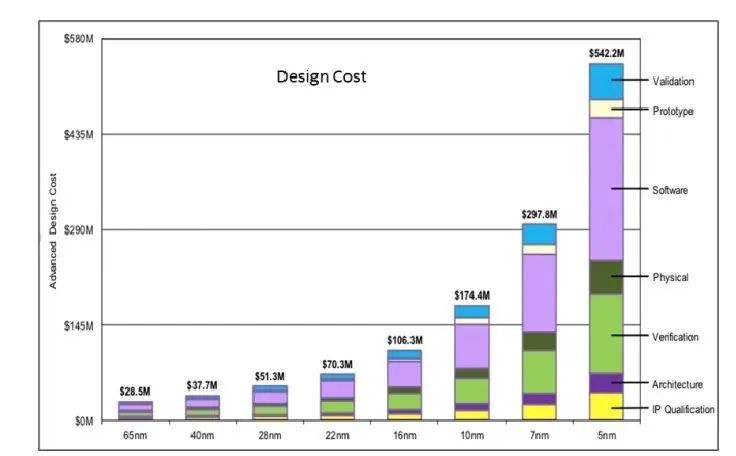

不同工艺节点的设计成本 (来源: IBS, 引自IEEEHeterogeneous Integration Roadmap)

在5nm以下工艺节点,芯片良率难题始终困扰着三星、台积电等头部晶圆代工厂。关于提升芯片良率,晶圆代工厂也在寻求更多方案突破瓶颈,例如采用EUV光刻机、3nm及以下节点采用GAA架构等。正因为采用了大量新工艺与新架构,芯片制造成本大幅增加,打破了摩尔定律经济效益的增长规律。

而Chiplet并不会受到工艺制程的制约,可以在系统内集成多个工艺节点的芯片,能够提高开发速度,降低整体成本。在芯片设计中,针对不同功能的系统模块,可选择性价比最高而不是最新的解决方案,部分功能单元还可实现复用,大幅提升了数据传输效率,降低了系统功耗,达成了经济效益与系统性能的最优解。

早在2019年,AMD便开始构建Chiplet产业生态,至今已陆续推出了Infinity Fabrie总线互联技术与针对存储芯片堆叠互联的HBM接口。去年,AMD又联合台积电开发用于CPU的3D封装技术,为高性能计算产品构建3D Chiplet架构。无独有偶,英特尔也于2019年推出Co-EMIB技术,实现多个Foveros芯片互连。基于英特尔嵌入式多芯片互联桥,英特尔已经实现了多款处理器芯片的设计与量产。除了英特尔与AMD外,英伟达、Marvell、台积电等一系列国际头部厂商,以及芯动科技、芯原股份、长电科技等国内企业,都纷纷涌入Chiplet赛道,积极布局Chiplet技术。

推动Chiplet互联标准统一

作为延续摩尔定律的关键,Chiplet的发展离不开完善开放的产业生态,而构建产业生态的核心则是在封装技术持续创新的同时,实现互联接口标准的统一。对于不同来源的芯片,其芯片架构与工艺各不相同,但通过统一的接口协议,便可实现芯片与芯片的互联互通,对于构建Chiplet产业生态有着重要推动作用。

实际上,半导体产业对于Chiplet接口标准的推进由来已久,但由于各种原因一直尚未能普及开来。2020年,英特尔便免费开放了AIB互连总线接口许可,以此推动Chiplet生态系统的建设。去年5月,国内也开始推动Chiplet接口总线技术标准制定工作,且已经完成了方案起草,进入意见征求阶段。

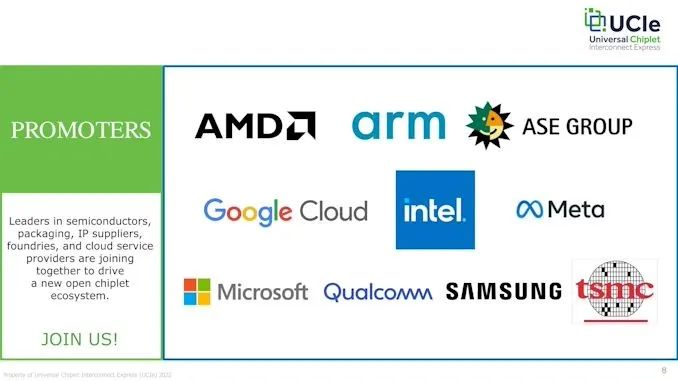

今年三月,由英特尔牵头,包括AMD、Arm、高通、三星、台积电、日月光,以及Google Cloud、Meta、微软等在内的国际大厂,宣布成立UCIe产业联盟,并推出了UCIe 1.0规范。这也意味着开放统一的Chiplet互联标准终于得以建立,提供了高带宽、低延迟、高功率、高效能的芯片封装互连。

UCIe产业联盟初始成员

随着Chiplet标准协议的推进,芯原股份、芯动科技、芯耀微等国产企业也陆续加入UCIe产业联盟,积极推进Chiplet技术国产化应用落地。其中,芯动科技还率先推出了国产自主研发物理层兼容UCIe标准的IP解决方案Innolink Chiplet,实现了跨工艺、跨封装的Chiplet互连方案。

总结

据Omdia预测,截至2024年,全球Chiplet市场规模将达到58亿美元,到2035年将进一步增长至570亿美元。随着芯片架构不断创新、工艺制程与先进封装逐渐成熟,Chiplet技术成本将进一步下降。Chiplet标准统一之后,芯片设计逐渐趋于简化。对于大规模芯片,Chiplet能够降低设计门槛,模块化设计也使得芯片验证流程得到优化,大幅提升了芯片可靠性。