三星谈3nm与DTCO

来源:内容由半导体芯闻(ID:MooreNEWS)综合自三星,谢谢。

来源:内容由半导体芯闻(ID:MooreNEWS)综合自三星,谢谢。

Samsung Foundry 于今年4 月举行的 CICC(定制集成电路会议)上发表了一篇关于设计技术协同优化的论文,即优化 3 纳米工艺的 PPA 与 GAA 晶体管应用,通过这篇文章,三星希望能够帮助大家更好地理解即将量产的 3nm GAA 相关的技术。

三星表示,半导体芯片是众多晶体管的集合体。因此,在我们详细介绍之前,让我们先谈谈作为半导体芯片基础的晶体管。

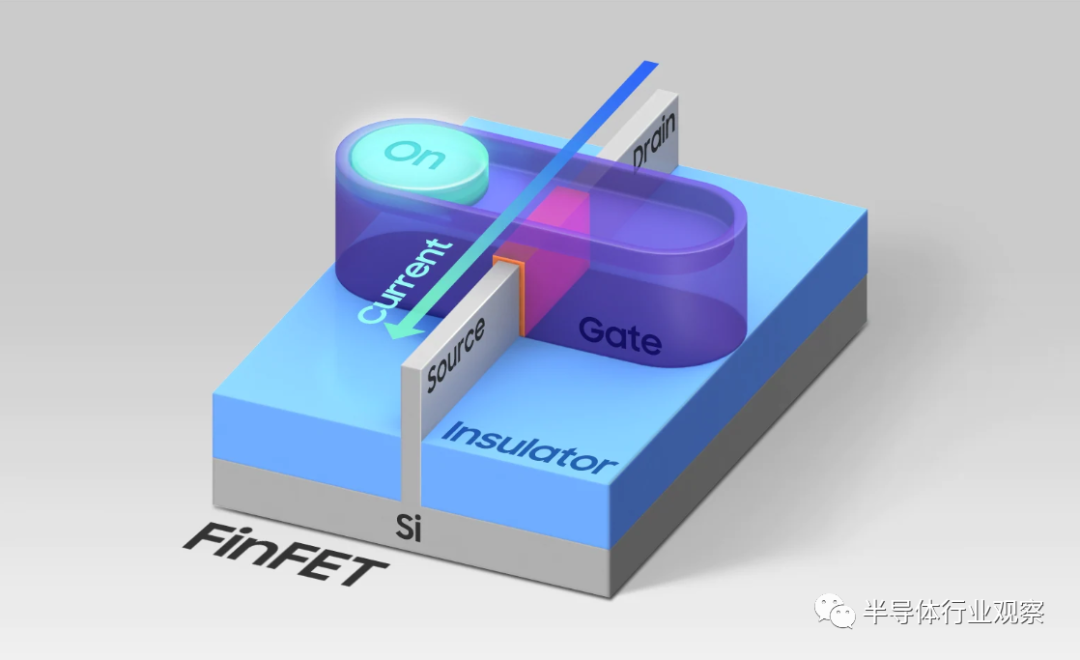

晶体管是一个小开关。由于开关操作是指从按下开关到使用电流打开和关闭灯的整个过程,而不是简单地按下开关,因此晶体管操作是指当晶体管达到电流流动阶段的过程导通,当晶体管关断时电流不流动。电压是开启晶体管的关键力量。当通过施加电压打开电流通路时,电流从电压高的地方流向电压低的地方。这类似于当用力打开水闸时,水如何在通道中从压力高的地方流向压力低的地方。

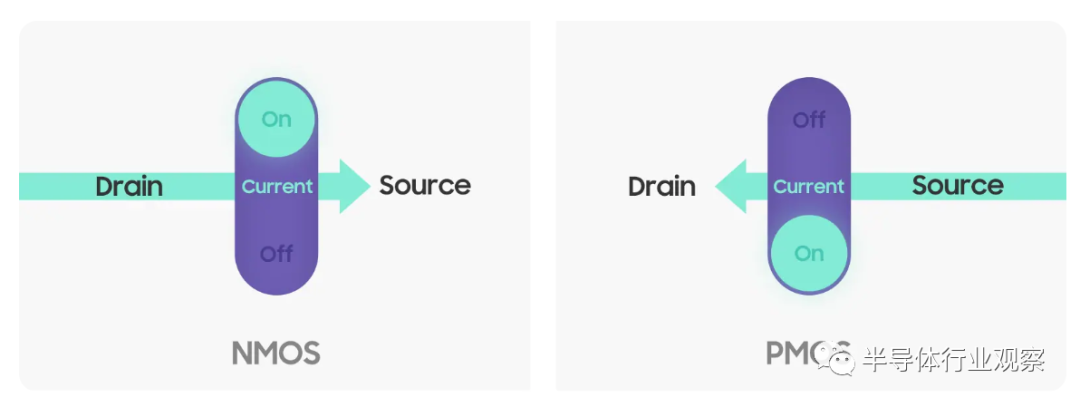

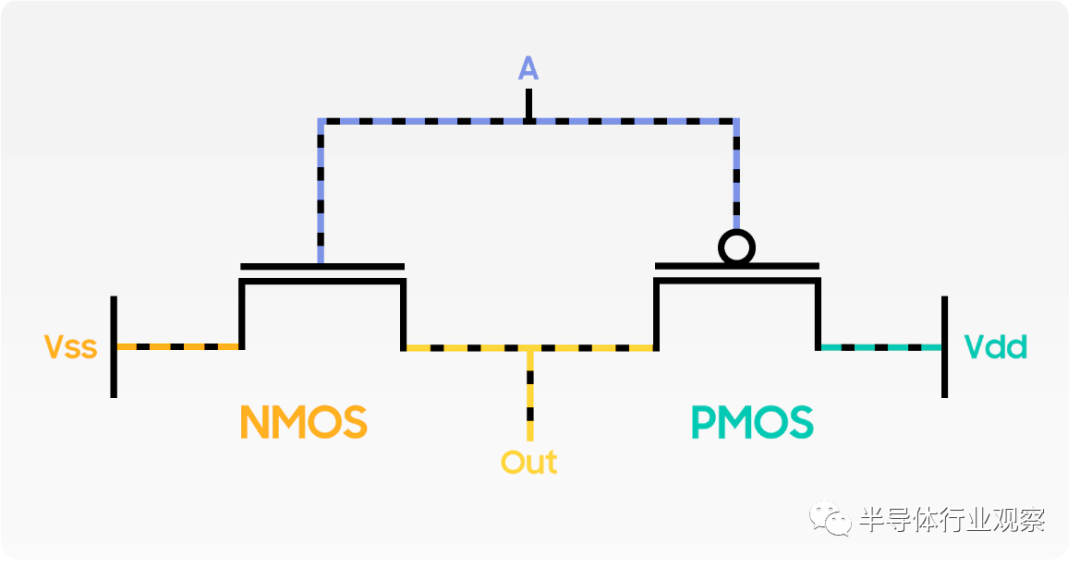

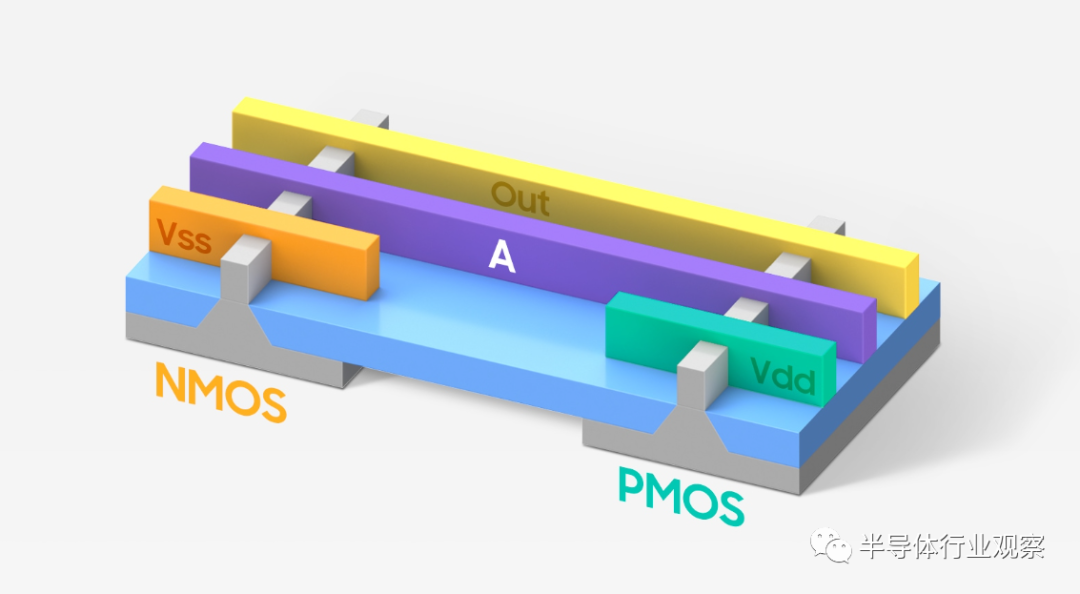

晶体管分为两种,NMOS和PMOS。晶体管的 Si 场(图 [1] 中的灰色区域)电压绝对值高的区域称为漏极,低值的场称为源极。参见图[1]和图[2]

图[1] NMOS晶体管结构与开关比较:当晶体管通过向栅极施加一定量的电压而导通时,电流从电压高的漏极流向电压低的源极。

图 [2] NMOS 和 PMOS 晶体管操作:PFET 通过使用负电压以与 NMOS 相反的方式工作。当负电压施加到栅极时,它开始工作。漏极电压也为负,因此电压电平低于源极电压。因此,电流从源极流向漏极。

如果是这样,我们为什么要把晶体管做得更小,把更多的晶体管放在一个芯片上呢?

如前所述,晶体管处于开启或关闭状态。假设晶体管开启状态为1,关闭状态为0,则可以通过晶体管表示由0和1组成的许多二进制代码。此外,可以使用二进制代码运行各种计算。通过这些计算,可以实现各种功能。更小的晶体管使我们能够实现更多样化的功能或制造具有相同性能水平的更小芯片。

那么,晶体管只需要很小吗?让我们再次以开关为例。如果打开和关闭一个开关需要不必要的“大力”,我们不能说这个开关是一个好的开关。同样,一个晶体管,如果一个晶体管需要过大的电压来让相同的电流流过,就不能被认为是一个性能良好的晶体管。如果开关打开时灯亮得晚,或者开关关闭时灯继续亮,则该开关也不是一个好的开关。在晶体管的情况下,我们说低速或让漏电流流动的晶体管是性能低的晶体管。

如果是这样,那么好的晶体管就是体积小、功耗低、性能高的晶体管。三个条件称为 PPA(性能、功率和面积)。高性能、低功耗、小面积晶体管的技术不断发展。

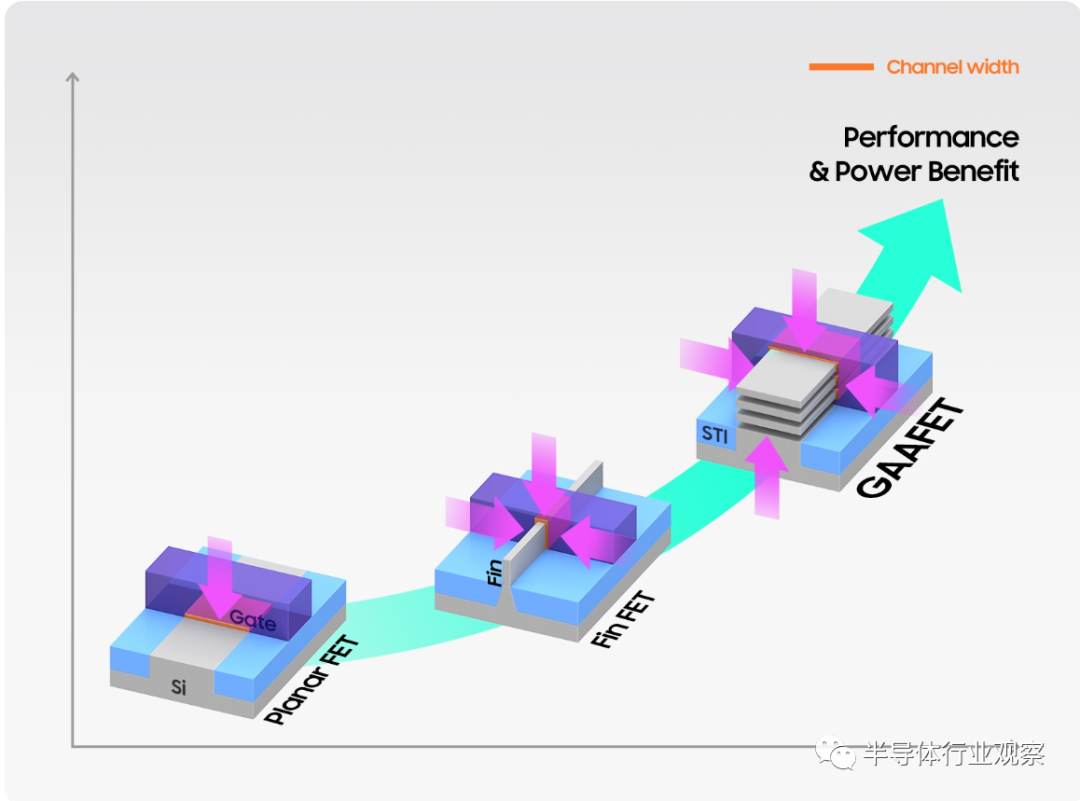

为了获得最好的 PPA,我们不仅使晶体管更小,而且还改变了结构。在晶体管中,电流流过图 [1] 中栅极和 Si(灰色区域)之间的接合面。我们称这段通道为沟道。我们改变了结构,使通道形状更有效。

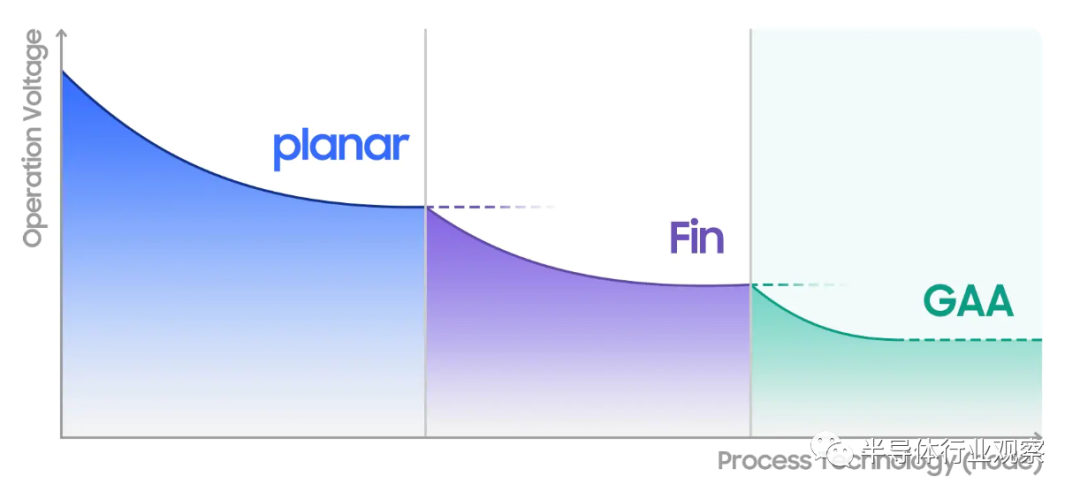

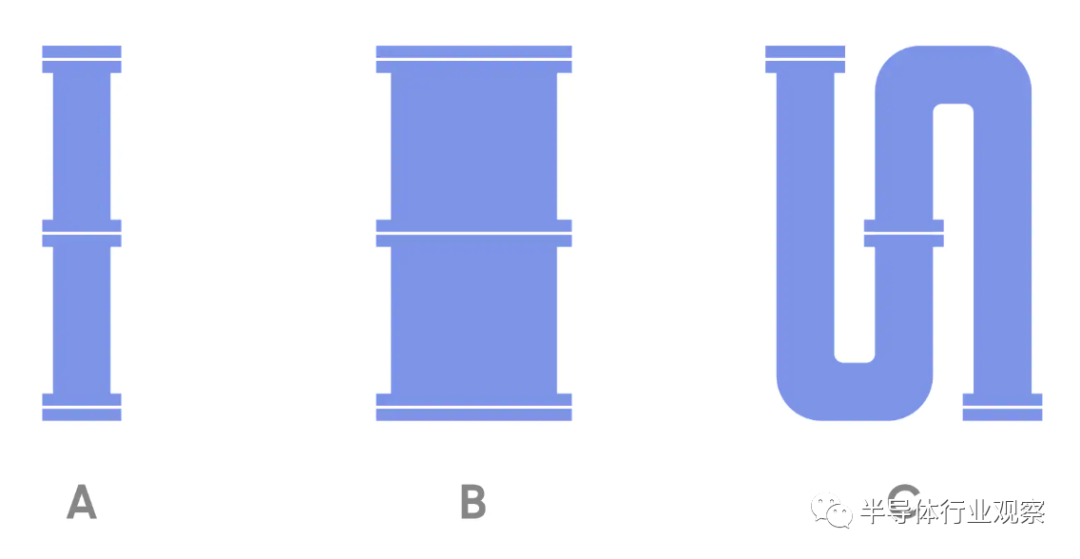

如图 [3] 所示,我们引领了三种类型的结构变化。随着沟道宽度和边数的增加,栅极控制沟道的能力也提高了。特别是对于平面型FET,随着尺寸变小,漏极和源极之间的距离,即沟道长度会减小,从而导致不需要的效应(短沟道效应)。我们通过开发 FinFET 结构来解决这个问题,以允许栅极包裹沟道,这可以改善其控制。

此外,我们通过增加允许更多电流流动的沟道宽度来扩展电流流动沟道。此外,GAA 是在侧面铺设 FinFET 的鳍片(Si 场像鱼鳍一样隆起的区域)的片状结构。将这些薄片垂直堆积起来,我们可以使更大的电流在具有相同水平面积的晶体管中流动。

图 [3] 通过晶体管结构变化提高性能和功率

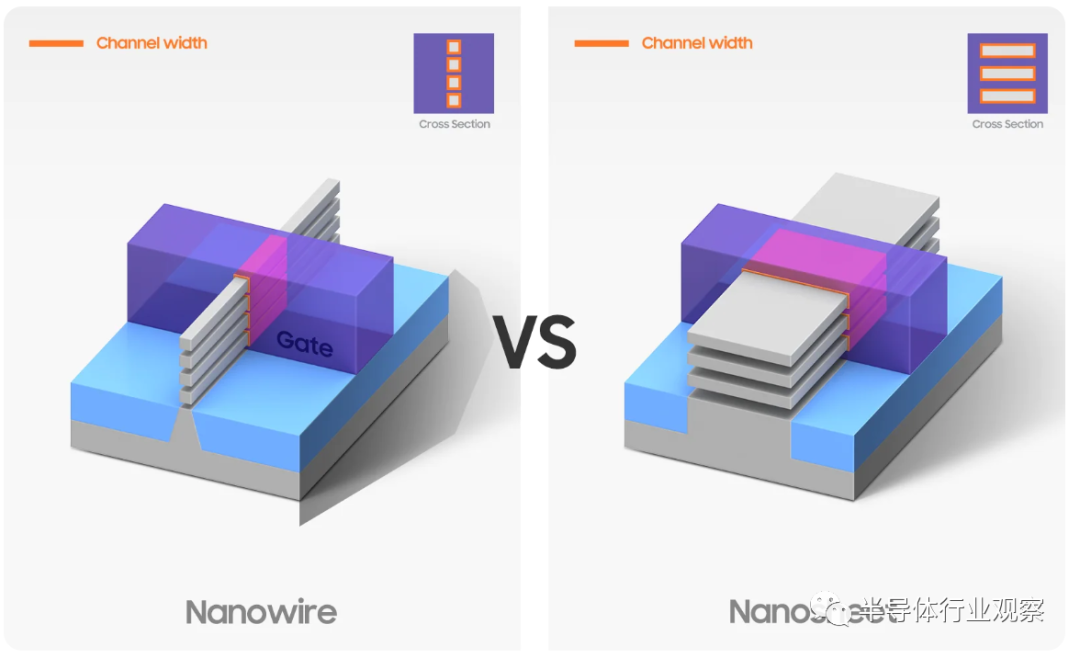

如图 [4] 所示,GAA 在结构上分为两种类型,线型和片型。对于纳米线GAA,必须堆叠更多的线层以增加总沟道宽度,这使得工艺更加复杂。为了克服这个问题,三星采用了具有更大宽度的片状结构的GAA——MBCFET™,而不是“线”。

图 [4] 纳米线和纳米片结构

通过将晶体管施加的电压乘以流过的电流来计算功率(功耗)。晶体管工作所需的电压称为工作电压。我们一直在不断努力通过降低工作电压来提高电源效率。这个概念类似于可以使用较少功率打开灯的开关如何更有效。

对于 MBCFET™,我们通过结构改变改进了开关特性(开关控制能力),使所有四个侧面都成为沟道。与具有改进功能的水龙头一样,仅使用少量功率即可关闭水,开关特性的改进使晶体管即使在低电压下也能正常工作。结果,工作电压降低,从而带来更高的功率效率。

图 [5] 工作电压随工艺技术发展的变化

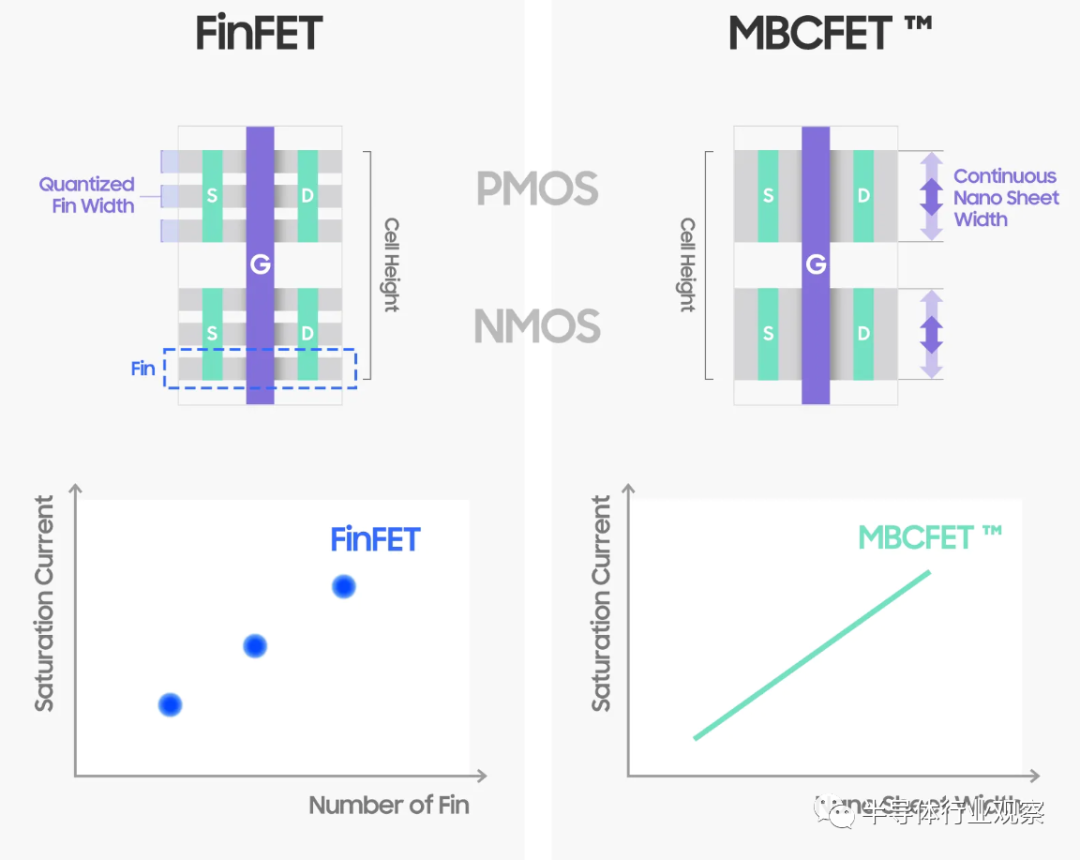

我们需要根据设计制造具有不同电流量的晶体管。要调整电流量,需要增加或减少沟道宽度。采用 FinFET 结构,无法调整被栅极包围的鳍片的高度。因此,为了增加整体沟道宽度,我们采用了一种方法,即在水平方向上增加鳍片的数量。然而,这种方法只能调整不连续的通道宽度。这是因为,当被栅极包围的鳍的沟道宽度为α时,宽度只能以α的倍数减小或增加。

与 FinFET 高度不同,MBCFET™ 允许通过控制片宽来连续调整通道宽度,如图 [6] 所示。

图 [6] FinFET 和 MBCFET™ 沟道宽度调整以及根据调整的电流变化

尽管所有 PPA 都在随着结构的变化而改进,但要利用这些优势具有足够的挑战性。这是因为芯片中聚集了许多晶体管,设计布局会影响这些 PPA,并且需要权衡性能、功率和面积。例如,如果它们之间有一堵墙,即使是一个小开关也不能靠近放置。

此外,带有更长和更复杂连线的更多开关会增加电阻并降低速度。如果我们不能同时拥有它们,我们别无选择,只能在给定的情况下找到最佳条件。我们必须找到一种在不降低性能的情况下减小尺寸的方法,一种在相同尺寸下提高性能的方法,或者一种使用少量功率产生相同性能的方法。我们把从过程和设计的角度寻找最优的过程称为DTCO(Design-Technology Co-Optimization)。DTCO 是一个整体流程,从工艺和设计两方面寻找最佳点。

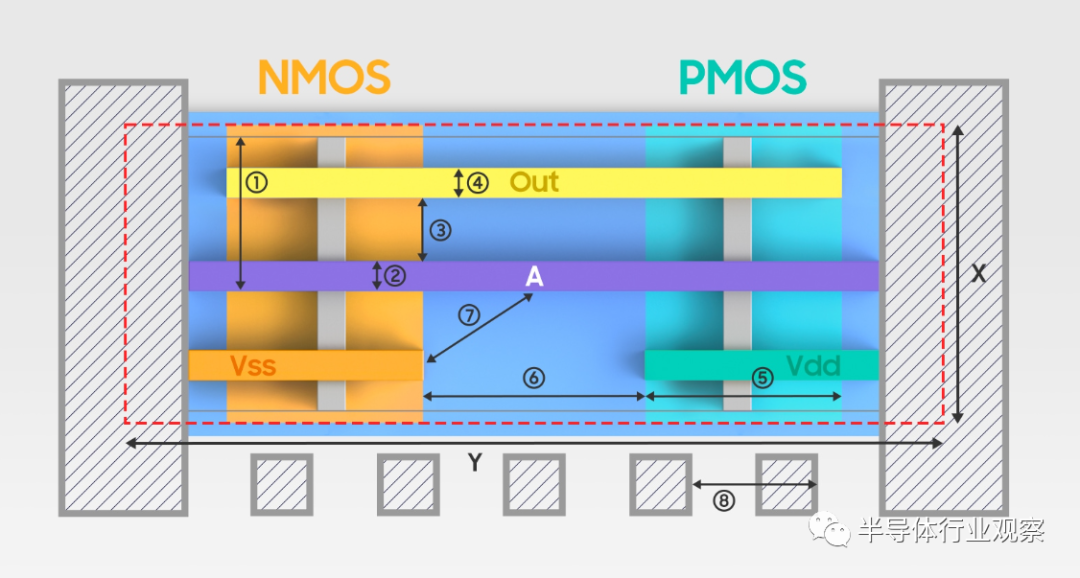

首先,我们从面积的角度来谈谈DTCO。简而言之,这是一项以减少面积为重点的活动。此外,它还找到了一种减少面积的解决方案,同时最大限度地减少功率溢出或性能下降。请看下图[7]、图[8]、图[9]。

图 [7] 由两个晶体管组成的电路图

图 [8] 根据电路图搭建的 FinFET 结构晶体管

图[9] FinFET结构晶体管布局(俯视图)

减少面积的最简单方法是将图 [9] 中所有元素的大小从 1 最小化到 8。然而,这些元件中的每一个都需要最小的面积来实现它们的用途和工艺能力,而这些变化会改变影响性能的因素(电阻和电容)。因此,DTCO 通过考虑流程和设计来执行确定最佳尺寸和距离的活动。换言之,DTCO 是通过优化确保最小化区域的过程。

前文有提到,功率是电压和电流的乘积。功率与性能密切相关。良好的性能是指通过让大量电流流过可以提高电路运行速度的状态。但是,性能与功率之间存在权衡关系。需要大量的电压才能让大量电流流动或更有效地控制电流。就像打开渡槽需要比水龙头更大的力一样。

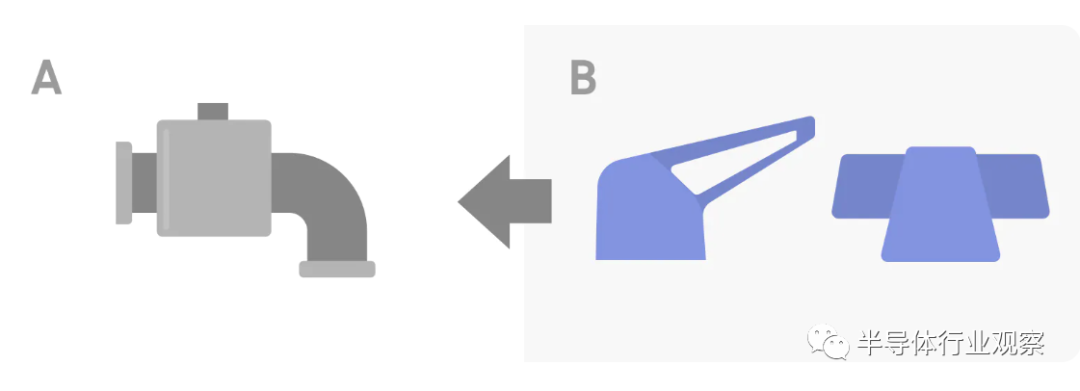

但是,我们需要一种方法来降低功耗,同时保持相同的性能水平。图[10](a)中的水龙头似乎需要非常大的力才能打开和关闭它。然后,我们需要用什么力来打开和关闭这个水龙头?我们需要一个可以帮助我们的物品,例如图 [10] (b) 中的把手和杠杆。

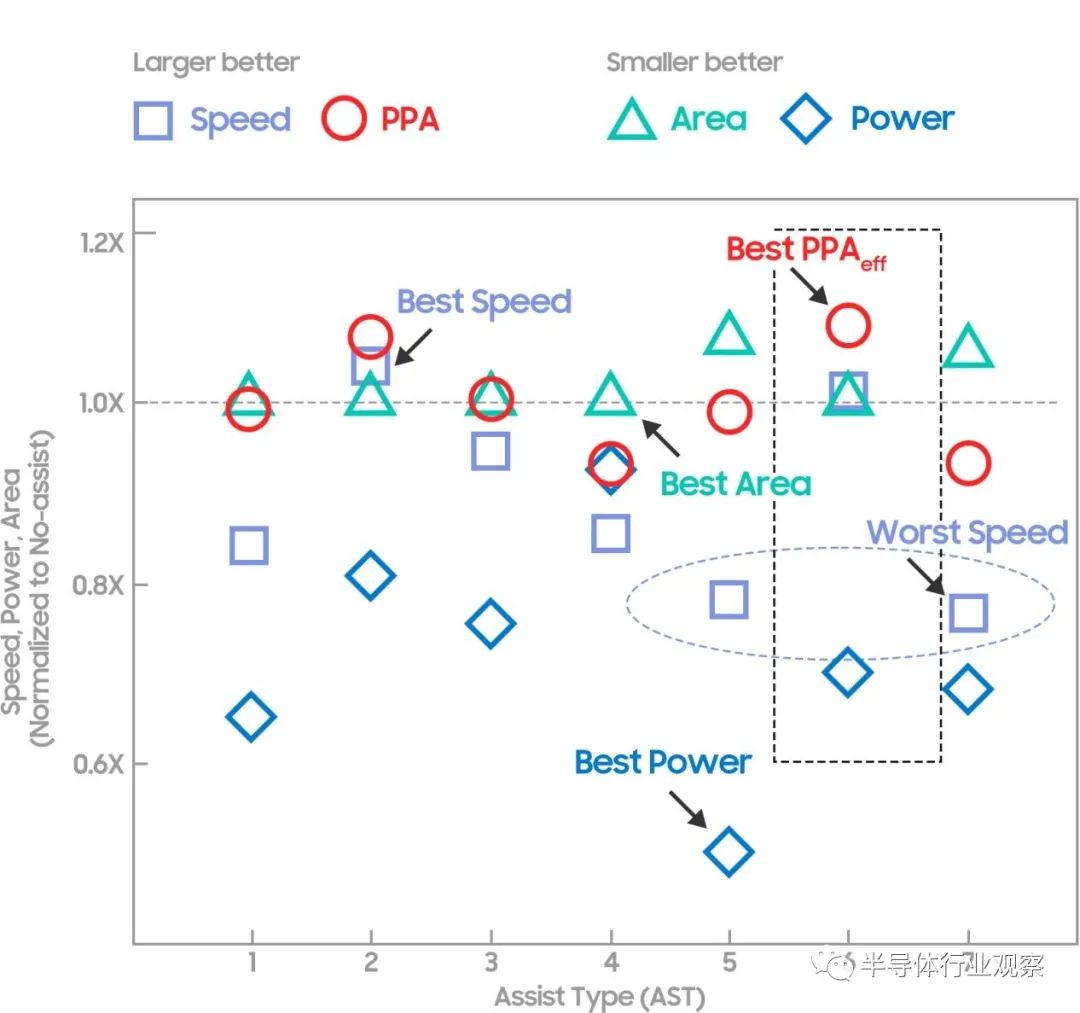

在芯片设计中也是如此。一个芯片要在低电压下提供适当的功能,并且每个晶体管都能成功运行,它需要辅助电路。然而,由于即使水龙头把手也有不同的形状和材料,这些附加元件也具有不同的 PPA 强度。通过 DTCO,我们正在寻找和应用辅助电路以确保最佳 PPA。这是一个寻找优化的最低功率的过程。

图[11] 由于即使水龙头把手具有不同的形状和材料,这些附加元素也具有不同的 PPA 强度。通过 DTCO,我们正在寻找和应用辅助电路以确保最佳 PPA。这是一个寻找优化的最低功率的过程。图[11] 由于即使水龙头把手具有不同的形状和材料,这些附加元素也具有不同的 PPA 强度。通过 DTCO,我们正在寻找和应用辅助电路以确保最佳 PPA。这是一个寻找优化的最低功率的过程。

图 [10] 要打开水龙头 (A),需要辅助装置,例如 (B) 中的把手。

图 [11] 辅助电路的 PPA 分析

最后,我们来谈谈DTCO的性能。为保证高性能,需要通过DTCO尽量减少芯片设计过程中无意出现的影响性能的因素(电阻电容等)。让我们举一个抵抗的例子。当路径更长和更窄时阻力会增加,这会导致性能下降。就像如果渡槽更窄或更长,相同数量的水流过渡槽需要更长的时间,如图[12]所示。

图 [12] 与渡槽的阻力比较((b)中阻力最小,(c)中阻力最大)

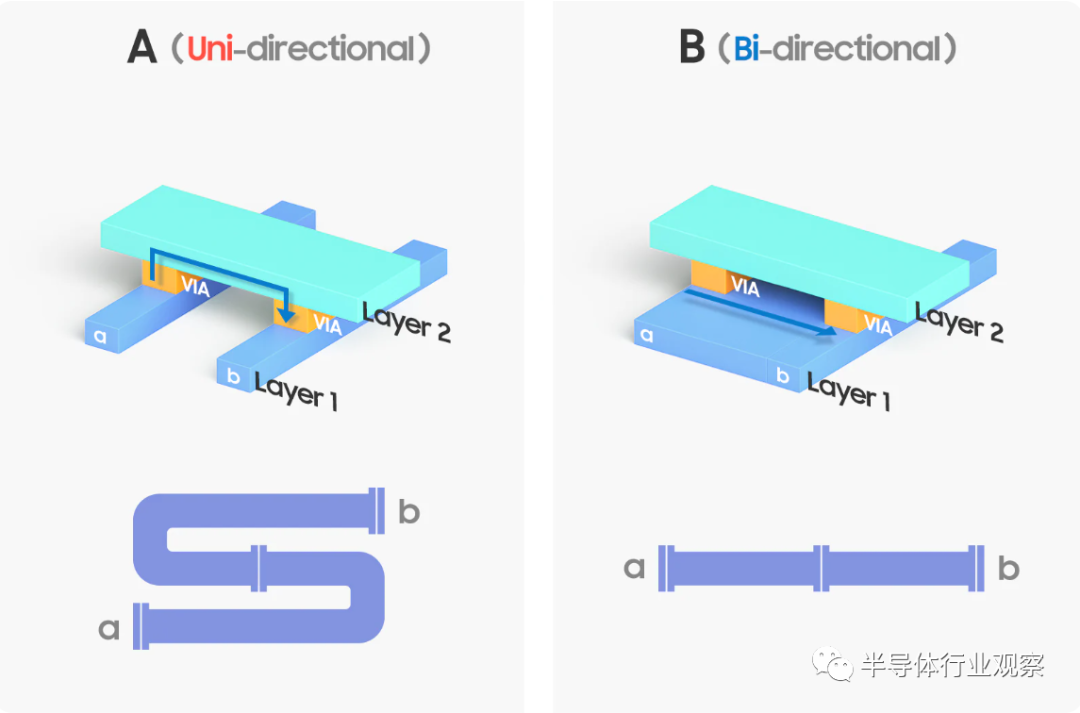

图[13]则显示了电流流动的路径,即布线。如上例所示,当电流从 A 流向 B 时,减少路径就是降低电阻,这可以提高性能。在图 [13] 的 A 中,蓝色层(第 1 层)和绿色层(第 2 层)只能分别提供纵向和横向的路径。这对于最短路径设置是不合逻辑的。然而,在(b)中,蓝色层(第 1 层)可以提供纵向和横向的路径。因此,可以使用短路径来降低电阻。

图 [13] (a) 每层提供单向路径 (b) 提供双向路径

随着晶体管变得越来越小,DTCO 活动的重要性也在增加。对于小而敏感的晶体管,即使是很小的变化也会产生重大影响。这就是为什么强调 DTCO 在 MBCFET 中的重要性。现在,让我们来看看 MBCFET 在 DTCO 方面的优势。

直截了当,MBCFET 具有为 DTCO 提供更多潜力的实力。这意味着限制晶体管中 DTCO 活动的因素已减少。让我们一一分析这些因素。

现有的晶体管,当沟道宽度增加或工作电压降低时,部分性能下降是不可避免的。这是因为,正如在前文中所解释的,它们是一种权衡关系。对于 MBCFET,我们通过降低性能恶化来增加 DTCO 活动的领域。

为了提高性能而增加沟道宽度可能会导致无意的性能损失。这意味着沟道宽度增加的效果并不完全导致性能提升。它是由结构元件之间发生的阻碍性能的因素(电阻和电容等)引起的。

简而言之,这是结构变化之后不可避免的现象。由于这种现象的规模取决于结构,因此结构的差异会导致性能损失的大小不同。FinFET 和 MBCFET 有很大的结构差异。既然如此,性能损失的大小也存在差异。

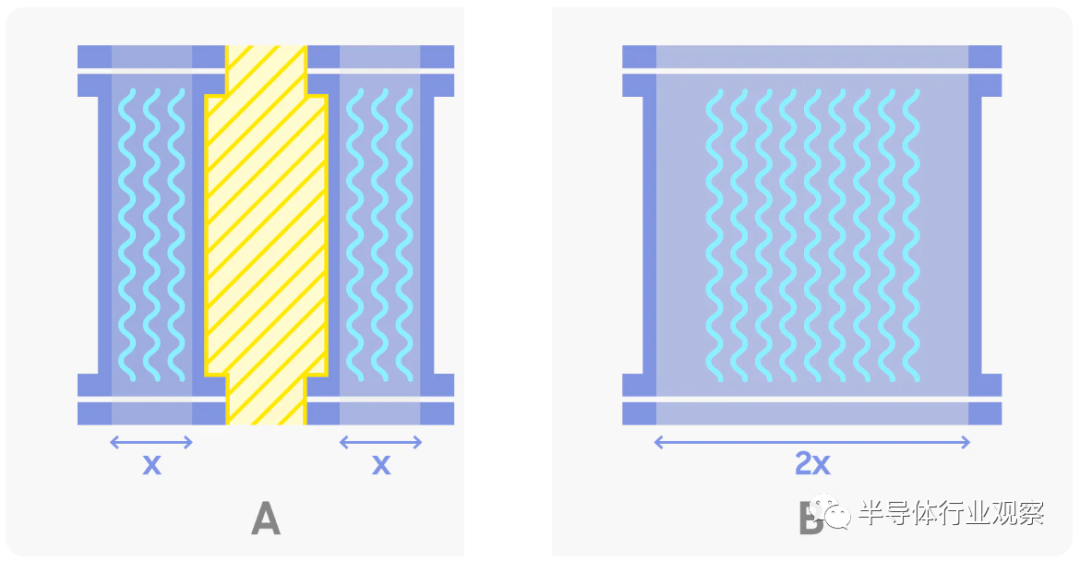

如前所述,FinFET 需要多一个鳍来增加沟道宽度。因此,与MBCFET相比,它涉及到更大的结构变化。在图[14]中,你可以看到,与增加一个渡槽( aqueducts)的宽度相比,建造另一个渡槽涉及形成不必要的结构(黄色区域),尽管两个渡槽的宽度相同。在 FinFET 中,更大的性能损失是由结构变化引起的。MBCFET 克服了这一限制,因为它不需要像鳍这样的额外结构来调整宽度。

图14:两种宽度相同的渡槽

解释了降低工作电压以实现低功耗的目标。还通过水闸和水龙头的示例解释说,低工作电压也会减少流动的电流量。然而,由于 MBCFET 具有比 FinFET 更宽的沟道,因此即使在低工作电压下,MBCFET 中流动的电流量也更大。这就像当水管本身更宽时,即使稍微打开水龙头也会流出更多的水。对于 MBCFET,通过让大量电流在低工作电压下流动,性能损失已降至最低。

减少变化带来的性能损失并不是全部。如前文所述,使用 MBCFET™ 可以连续调整沟道宽度。除了提供更符合设计所需水平的沟道宽度外,还有助于优化沟道宽度调整。

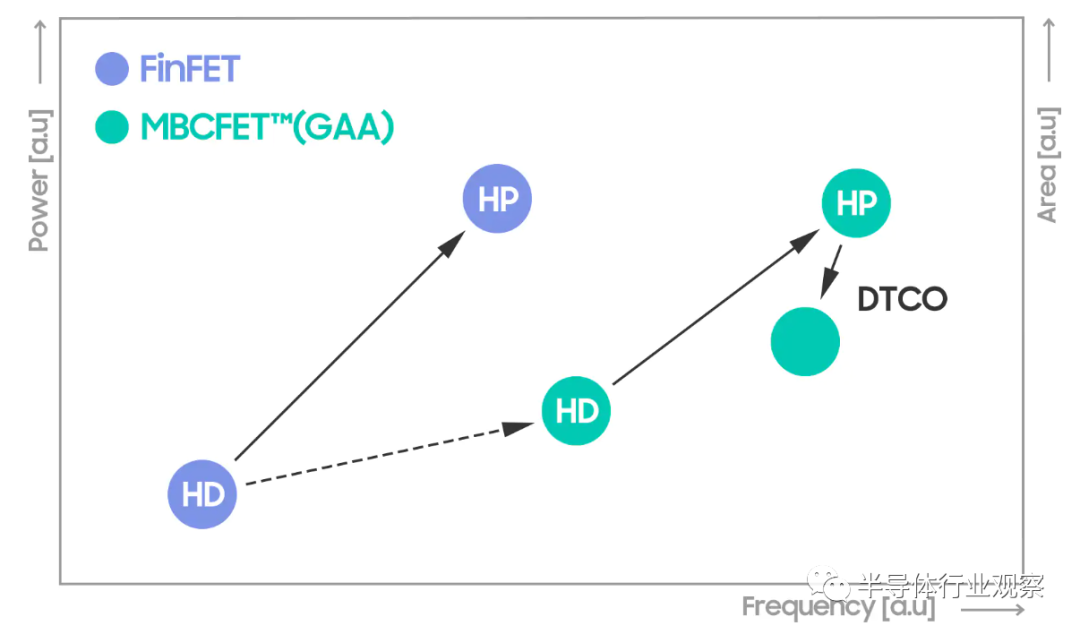

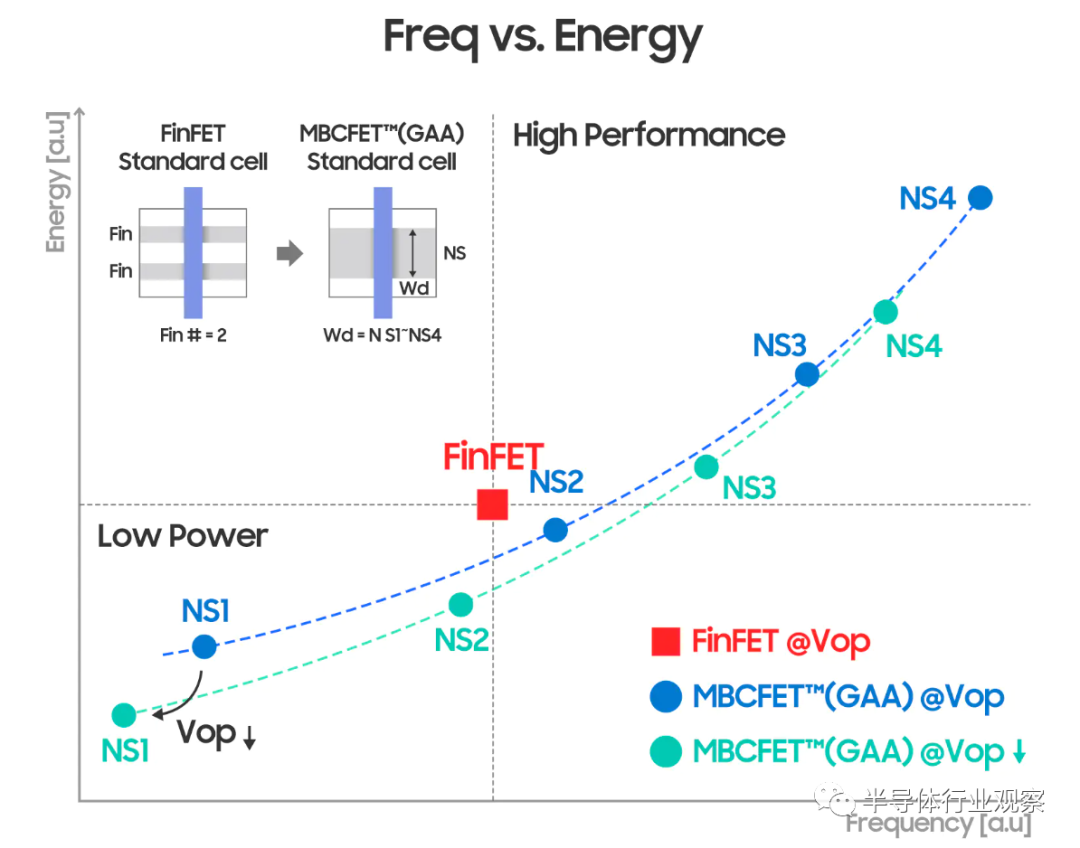

基于上述优点,DTCO 获得了更大的潜力。正如您在图 [15] 中看到的,MBCFET™ 与 FinFET 不同,它可以通过 DTCO 找到并转移到其简单活动范围之外的 PPA 领域。此外,如图 [16] 所示,可以使用从 NS1 到 NS4 的各种通道宽度和改进的性能。此外,通过降低工作电压,可以进一步降低功耗。

图 [15] 按设计目的划分的 PPA 水平(HD(高密度)/HP(高性能))

图 [16] 提供各种沟道宽度和性能选项的 GAA

在三星看来,其 MBCFET™ 为 DTCO 开辟了新的可能性,并正在实施它以帮助其客户尽可能体验 MBCFET™ 的 PPA 优势。MBCFET™ 的这一进步将为客户提供最佳工艺,它还使三星能够在其工艺中提供更大的支持。

参考链接

https://semiconductor.samsung.com/newsroom/tech-blog/gaa-dtco-for-ppa/

https://semiconductor.samsung.com/newsroom/tech-blog/gaa-dtco-for-ppa-part-2/

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3083内容,欢迎关注。

推荐阅读

半导体行业观察

『半导体第一垂直媒体』

实时 专业 原创 深度

识别二维码,回复下方关键词,阅读更多

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装

回复 投稿,看《如何成为“半导体行业观察”的一员 》

回复 搜索,还能轻松找到其他你感兴趣的文章!