三星全球首发3纳米,领先台积电

6月30日,在今年上半年的最后一天,三星电子正式宣布,基于3nm全环绕栅极(Gate-All-AroundT,简称 GAA)制程工艺节点的芯片已经开始初步生产。

图源:三星半导体

而就在上周,韩媒ekn就曾报道,有业内人士称,三星电子有望在这周内正式宣布下一代基于GAA的3纳米半导体工艺量产。当时报道显示,如果三星电子计划上半年量产成功,将能够在技术上超越其竞争对手台积电。

从当前的消息来看,三星在3nm 量产进度上确实已经快人一步,成为全球首家3nm 量产代工厂,但这场3nm之战的胜负真的已经揭晓了吗?

性能提升,PPA优势最大化

三星电子官方消息显示,三星电子首次实现GAA“多桥-通道场效应晶体管”(简称: MBCFET Multi-Bridge-Channel FET)应用打破了FinFET技术的性能限制,通过降低工作电压水平来提高能耗比,同时还通过增加驱动电流增强芯片性能。

据悉,三星首先将纳米片晶体管应用于高性能、低功耗计算领域的半导体芯片,并计划未来将其扩大至移动处理器领域。

图源:三星半导体

与采用窄通道纳米线的GAA技术相比,3nm GAA技术采用了更宽通的纳米片,能提供更高的性能和能耗比。在3nm GAA技术上,三星能够调整纳米晶体管的通道宽度,优化功耗和性能,从而能够满足客户的多元需求。

此外,GAA的设计灵活性对设计技术协同优化(DTCO)²非常有利,有助于实现更好的PPA优势。与三星5nm工艺相比,第一代3nm工艺可以使功耗降低45%,性能提升23%,芯片面积减少16%;而未来第二代3nm工艺则使功耗降低50%,性能提升30%,芯片面积减少 35%。

三星电子还表示,为了满足IC设计师们所面对的处理海量数据、更多验证功能,以及扩展更紧密复杂产品的挑战,三星致力于提供更稳定的设计环境,以帮助减少设计、验证和批准过程所需的时间,同时也提高了产品的可靠性。

三星电子将与包括ANSYS、楷登电子、西门子和新思科技在内的三星先进晶圆代工生态系统SAFE™(Samsung Advanced Foundry Ecosystem)合作伙伴一起,提供3nm设计基础设施和服务。

何为GAA

GAA——(Gate all around Field Effect Transistors,GAAFET),又称全环栅晶体管,是一种继续延续现有半导体技术路线的新兴技术,可进一步增强栅极控制能力,克服当前技术的物理缩放比例和性能限制。

据了解,GAAFET有两种结构,一种是使用纳米线(Nanowire)作为电子晶体管鳍片的常见GAAFET,另外一种则是以纳米片(Nanosheet)形式出现的较厚鳍片的多桥通道场效应管MBCFET,这两种方式都可以实现3nm,但取决于具体设计。从GAAFET到MBCFET,可以视为从二维到三维的跃进,能够改进电路控制,降低漏电率。

按照专家观点:GAA晶体管能够提供比FinFET更好的静电特性,可满足某些栅极宽度的需求。这主要体现在同等尺寸结构下,GAA沟道控制能力增强,给尺寸进一步微缩提供了可能;传统FinFET的沟道仅三面被栅极包围,而GAA以纳米线沟道设计为例,沟道的整个外轮廓都被栅极完全包裹住,意味着栅极对沟道的控制性能就更好。

Leti公司高级集成工程师Sylvain Barraud指出:“与FinFET相比,除了具有更好的栅极控制能力以外,GAA堆叠的纳米线还具有更高的有效沟道宽度,能够提供更高的性能。”

由于GAAFET 晶体管只在先进制程中有所采用,所以能参与其中的只有三星、台积电、和英特尔三家巨头。

三星自称在2002 年就对GAA 保持关注并投入研究,并于2019年宣布,将在3nm制程世代,改采GAA技术,作为FinFET之后的接班制程。根据三星的说法,与7nm制造工艺相比,3nm GAA技术的逻辑面积效率提高了45%以上,功耗降低了50%,性能提高了约35%。

今天,三星电子3nm量产的官宣也让三星成为全球首家量产3nm的企业。

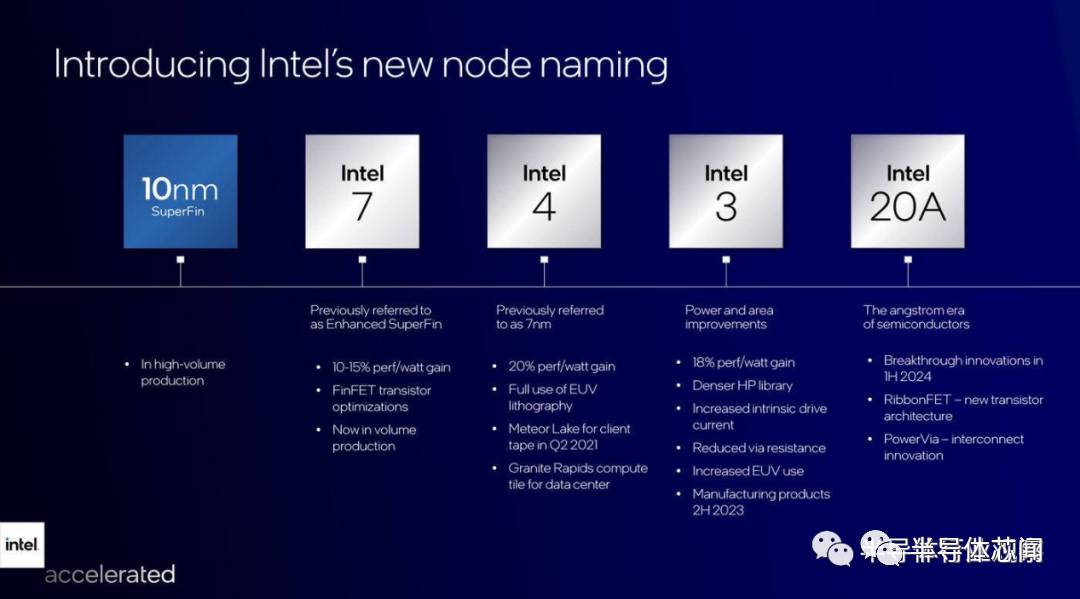

英特尔方面,2020年年初《Profesionalreview》曾报导,英特尔在5纳米节点上将会放弃FinFET电晶体,转向GAA环绕栅极电晶体。不过从英特尔去年公布的未来五年的芯片制程工艺的技术路线图来看,预计要在2024年的Intel 20A(相当于我们说的2nm)制程上才会用到RibbonFET即英特尔的GAA技术。

图源:英特尔

对于台积电2nm制程将采用GAA晶体管好像已成产业内默认的事实,不过笔者搜寻资料发现,台积电官方关于2nm并未给出明确的说法,最初是在2020年7月,据台湾经济日报报道,台积电2nm技术研发有重大突破,已成功找到路径,将切入GAA技术。而在日前2022年第一季度财报电话会议上,虽然台积电总裁魏哲家透露2nm计划2024年预生产,2025年投产,但当分析师询问“有关在 N2 上台积电首次使用 GAA FET,逐渐取代 finFET”的问题,魏哲家也是避而不答。

不过台积电(南京)有限公司总经理罗镇球曾在去年年底透露,台积电研发 Nanosheet / Nanowire 的晶体管结构(类似 GAA)超过 15 年,已经达到非常扎实的性能。

台积电2nm是否真的采用GAA,或许只能交给时间来揭开这个谜底。

3nm之战胜负已分?

当前3nm之战主要围绕的对象仍然是台积电和三星。自从芯片制造进入先进工艺制程,台积电就率先量产了7nm、5nm工艺,到了如今3nm阶段,虽然曾有消息称台积电在其 3nm 工艺良率方面存在困难,工艺很难达到令人满意的良率,但台积电总裁魏哲家在2022年Q1情况说明会上明确指出,预估3nm将于今年下半年出货,2023年大规模量产。而N3E制程将在3nm量产一年之后投产,目前研发进度超出预期,可能提前投产。

但在3nm量产时间方面,显然这次由三星拔得头筹。早在去年6月,三星就宣布了基于GAA晶体管芯片的流片。而就在今年2月,三星电子就在财报中展望2022年二季度的表现时提到,“将通过在世界上首次量产3nm制程(GAA 3-nano)来提高技术领先地位”。从时间上来看,三星电子也确实做到了3nm 二季度量产。

此外,三星代工市场战略团队负责人 Moonsoo Kang 也曾表示,“2022 年上半年,第一代 GAA 工艺量产,3GAE(3nm Gate-All- “Around Early”已经结束,未来我们将继续按计划开发第二代GAA工艺“3GAP(3nm Gate-All-Around Plus)”。

不过,台媒《经济日报》对此表示,三星虽然宣称3nm即将量产,但从晶体管密度、功耗等关键指标看,三星的3nm实际上与台积电的4nm及英特尔的Intel 4(原英特尔7nm)制程相当,且良率可能存在问题。

此前,韩媒曾报道,三星缺乏3 纳米GAA 制程相关专利,令三星感到不安。但也有业内人士表示,“三星官方宣布量产3纳米,意味着它已经确保了一定的良率。”

在客户方面,据外媒报道,一家中国矿机芯片公司将成为三星电子3nm制程的首位客户,高通也预定了三星电子的3nm制程。而台积电方面,据台湾电子时报 6 月 23 日援引业内制造商消息,包括 AMD、苹果、博通、英特尔、联发科、英伟达和高通等台积电的主要客户均在排队等待 3 纳米工艺的产能。

在产能方面,三星电子作为存储半导体的绝对强者,在代工市场一直追赶台积电。近期,与台积电的市场份额差距也在拉大。根据台湾市场研究公司TrendForce的数据,三星电子今年第一季度的代工销售额为53.28亿美元(约合6.4256万亿韩元),比去年第四季度下降3.9%。在全球前10大晶圆代工企业中,三星电子是唯一一季度销售额落后的企业,其市场份额在此期间也从18.3%下降至16.3%。另一方面,台积电同期销售额增长11.3%至175.29亿美元,市场份额从52.1%提升至53.6%。三星一直试图通过首先确保超精细工艺技术来撼动由台积电主导的代工市场。

正是在这种背景下,李在镕副委员长最近从欧洲出差归来,强调了技术的重要性,并表示“一是技术,二是技术,三是技术”。三星电子计划加快“System Semiconductor 2030 Vision”,以3nm量产为契机,在系统半导体领域跃居世界第一。三星电子将投资 170 亿美元在德克萨斯州泰勒建造的第二家代工厂也已开始建设。Taylor Sea Foundry Plant占地约500万平方米(150万坪),目标是2024年下半年投产,建成后将生产最先进的系统半导体。

台积电则有外媒在报道中称,台积电 3nm 制程工艺试产进展顺利,量产初期的月产能,预计将超过 2.5 万片晶圆。其中新竹科学园区 3nm 工艺量产初期的月产能预计在 10000-20000 片晶圆,台南科学园区预计为 15000 片晶圆。

总而言之,如今判定谁胜谁负还言之过早,未来仍是未知数。

发送给作者